Wonderful Info About What Is Lec In DFT

Understanding LEC in DFT

1. What Exactly Is LEC? It's Not a New Dance Move, I Promise!

Okay, let's get right to it. You're probably scratching your head wondering, "What in the world is LEC in the context of DFT?" Well, DFT stands for Design For Testability, which is all about making sure we can actually test the chips we design to make sure they're not duds. And LEC? That's Logic Equivalence Checking. Think of it as the meticulous accountant of the chip world, double-checking that everything adds up correctly.

Imagine you've baked a cake following a recipe. You think you followed the recipe perfectly, but how can you be absolutely sure? Logic Equivalence Checking is like having a friend who baked the same cake, but followed the recipe exactly as it's written. You compare your cake to theirs — is the shape the same? The texture? The taste? If they match, you can be pretty confident you did things right! In the chip design world, instead of cakes, we're comparing logical representations of the design.

More formally, Logic Equivalence Checking verifies that two different representations of a digital circuit perform the same logical function. This usually involves comparing a golden, verified version of the design (perhaps an RTL description) to a modified version (perhaps a gate-level netlist after synthesis or after ECO changes). If they're logically equivalent, it means the changes made during the design flow haven't introduced any unintended errors. No one wants a chip that thinks it's doing one thing, but is actually doing something completely different! Talk about a costly mistake!

So, LEC is a vital step in the design flow. It gives us the confidence to move forward, knowing that the chip we're about to manufacture will actually work as intended. It's like having insurance for your chip design, protecting you from unexpected (and often expensive) surprises down the road.

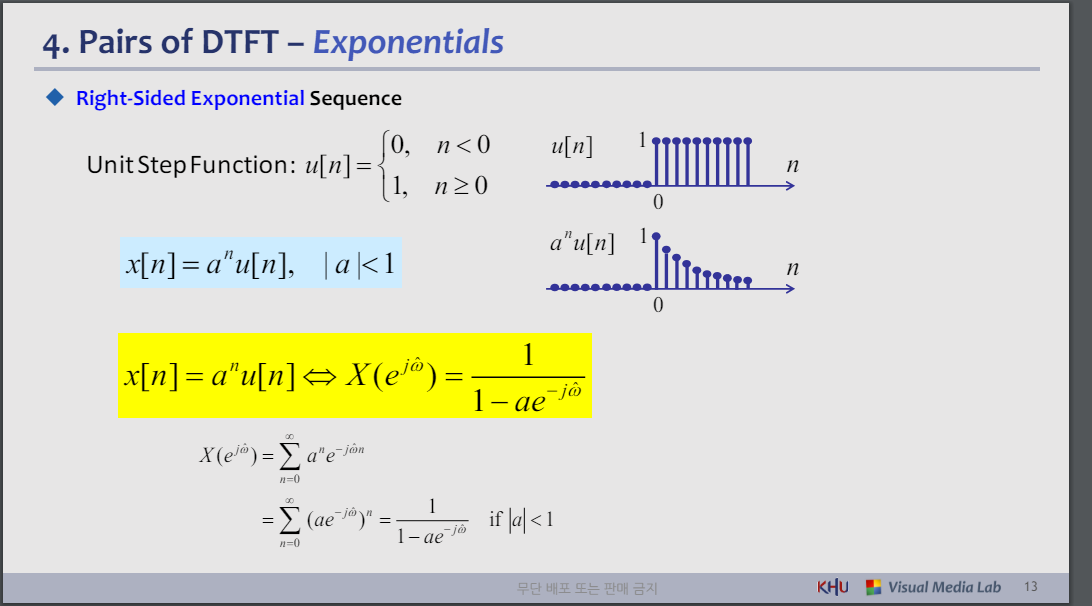

Lec.10c DTFT & DFT

Why Bother with LEC? The Case for Meticulousness

2. Avoiding Catastrophic Errors

You might be thinking, "Why all this fuss? Can't we just simulate everything really well?" Well, simulations are great, but they can't cover every possible scenario. LEC, on the other hand, provides a mathematical proof that two designs are equivalent. Think of it this way: simulation is like testing a few specific ingredients of the cake; LEC is like verifying that the entire recipe, from beginning to end, produces the same cake. A subtle difference in a single gate could have huge ramifications, and simulations may not catch it.

Consider the example of an Engineering Change Order (ECO). Say you have a fully verified chip design, but at the very last minute, you realize you need to fix a critical bug. You implement a change, but how do you know that change hasn't inadvertently introduced other errors? LEC allows you to compare the original design with the ECO'd design, ensuring that the only difference is the intended bug fix. It's a safety net for those late-stage changes that can often be the riskiest.

Furthermore, LEC helps verify the correctness of synthesis and place-and-route tools. These tools automatically convert high-level RTL code into a physical layout of transistors. While these tools are generally reliable, they're not perfect. LEC can catch errors introduced during the translation process, ensuring that the final layout accurately reflects the intended behavior of the RTL code. Think of it as double-checking the translator's work to ensure that the meaning of the original text hasn't been lost in translation.

Essentially, LEC provides a level of confidence that simulation alone simply can't achieve. It's a crucial step in ensuring the reliability and functionality of complex integrated circuits, protecting us from costly errors and delays. Ignoring LEC is like building a house on a shaky foundation it might stand for a while, but eventually, things will start to crumble. And in the world of chip design, that crumbling can be very expensive!

Lec.10c DTFT & DFT

How Does LEC Work? A Simplified Explanation

3. The Magic Behind the Scenes (Without Getting Too Technical)

Okay, let's dive into the general idea of how LEC works. It boils down to comparing the logical functions of two designs — the "reference" design and the "implementation" design. These designs are typically represented using Boolean equations or other logical representations. The LEC tool then attempts to prove that these two representations are logically equivalent.

One common approach is to use Binary Decision Diagrams (BDDs). A BDD is a graphical representation of a Boolean function, and it provides a canonical form for comparing different expressions. The LEC tool builds BDDs for corresponding outputs in the reference and implementation designs. If the BDDs are identical, the outputs are logically equivalent.

Another technique involves SAT solvers (Boolean Satisfiability solvers). The LEC tool constructs a Boolean formula that expresses the condition where the reference and implementation designs produce different outputs for the same inputs. The SAT solver then attempts to find a solution to this formula. If the SAT solver can't find a solution, it means the formula is unsatisfiable, indicating that the two designs are logically equivalent.

The key thing to remember is that LEC is all about proving logical equivalence through mathematical techniques. It's not just about running a bunch of simulations and hoping for the best. It's about providing a rigorous guarantee that two designs are functionally identical. And while the underlying algorithms can be complex, the fundamental goal is quite simple: to ensure that our chips do what we expect them to do.

Lec.10c DTFT & DFT

LEC in the Design Flow

4. The Right Place at the Right Time

So, where does LEC actually fit into the chip design process? Typically, LEC is performed at several key stages. One common stage is after logic synthesis, where the high-level RTL code has been translated into a gate-level netlist. LEC verifies that the synthesis process hasn't introduced any errors. Another stage is after place-and-route, where the gates have been physically laid out on the chip. LEC ensures that the layout process hasn't altered the functionality of the design.

LEC is also crucial after ECO changes. As mentioned earlier, ECOs are late-stage modifications to a design, and they can be particularly risky. LEC provides a way to verify that the ECO has only fixed the intended bug and hasn't introduced any new problems. Its akin to a quick check-up after surgery to make sure everything is healing as expected.

Many modern design flows incorporate LEC in an automated fashion, making it an integral part of the verification process. The LEC tool is often integrated into the design environment, allowing designers to run checks quickly and easily. This helps catch errors early in the design cycle, when they're much easier (and cheaper) to fix. Think of it as preventative maintenance for your chip design, catching small problems before they turn into big ones.

In summary, LEC is not a one-time event, but rather an ongoing process throughout the chip design flow. It's a critical component of a robust verification strategy, ensuring that the final chip meets its specifications and performs as intended. It's like having a quality control inspector at every stage of the manufacturing process, ensuring that the final product is flawless.

Lec.10c DTFT & DFT

Common LEC Challenges and How to Overcome Them

5. Navigating the Pitfalls

While LEC is a powerful tool, it's not without its challenges. One common challenge is dealing with large and complex designs. As chip designs become increasingly sophisticated, the computational complexity of LEC can increase dramatically. This can lead to long runtimes and memory limitations. Imagine trying to compare two incredibly intricate puzzles — the sheer size and complexity can be overwhelming.

Another challenge is handling sequential logic. LEC is generally more difficult for circuits with feedback loops and memory elements, as these introduce complex dependencies between different parts of the design. Special techniques are often required to handle sequential equivalence checking effectively. It's like trying to untangle a complicated knot — you need to understand the underlying structure to avoid making things worse.

To overcome these challenges, several techniques can be employed. One is to use abstraction techniques, which simplify the design by removing unnecessary details. Another is to partition the design into smaller, more manageable blocks. These blocks can then be checked independently. Imagine breaking that large puzzle into smaller sections — it becomes much easier to tackle.

Additionally, advanced LEC tools often incorporate sophisticated algorithms and heuristics to improve performance. These algorithms can exploit the structure of the design to reduce the computational complexity of the equivalence checking process. So, while LEC can be challenging, there are many strategies and tools available to help designers overcome these hurdles and ensure the correctness of their chip designs.